## Technical Paper

### **High Frequency Terminator Characterization and the SCSI Bus**

#### By

Dr. Yinggang Tu CTS Corporation 905 West Blvd. North Elkhart IN 46514

Phone: (574) 293-7511, Fax: (574) 293-6146

#### And

Barry Caldwell

Staff Design Engineer

Storage Components, HBA R&D

LSI Logic, Inc.

3718 North Rock Road

Wichita, Ks 67226

Phone: (316) 636-8000

Resistor networks, either passive or active, are widely used as the termination device of choice in SCSI bus topologies and play an important role in maintaining computer data bus transfer signal integrity. With the steady increase of microprocessor speeds, the design of data buses and termination devices is requiring a more exacting component selection and physical design methodology or practice. Present microprocessor speeds are reaching into the 1GHz range, while SCSI ultra4 appears with a data transfer rate of 320Mbyte and data clock rates of 160MHz. The edge rates of active bus devices used in digital circuits are now approaching speeds as low as 0.3ns with the slew rate on current generations of SCSI at 1nanosecond or less. The residual skew error may be as low as  $\pm 0.15$ ns. With the steady increase of speed, the skew rate budgets are become tighter and tighter. Parasitic effects of termination devices can no longer be considered negligible due to the physical circuit mismatch and uncertainty under the fast edge rate A problem here is that a termination device is usually characterized at low circumstance. frequencies and no information is provided about its parasitic parameters. As reasons mentioned above, it is of a great interest to evaluate those parasitic parameters to know its effects on digital circuit quantitatively as well as a means to validate and improve termination device performance.

Because the parasitic parameters existing in a resistor network have very low inductance and capacitance ranges measuring those parasitics can become a significant challenge. Traditionally a digital device or circuit is characterized using TDR (Time Domain Reflectometry) techniques in the time domain. But there are two barriers to overcome when using TDR techniques that remain unsolved. One is the dynamic range of TDR measurement system. The other is the technique to de-embedding the transition from test probe to DUT. The former will results in limitations in detecting small inductance and capacitance values. While the latter may cause hard-to-interpret measurement results especially in fast-rise-time measurement environments. Especially when inductance and capacitance are very low. Unfortunately no concrete approached has been found yet that can be resolved these two problems using TDR techniques [1].

In the frequency domain, the above mentioned obstacles can easily be removed by using a network analyzer and TRL (Through Reflection Line) calibration techniques. The network analyzer receiver used for this needs at least a 100 dB dynamic range, leading to a TRL technique that is ideal for the de-embedding measurement. The setback of the frequency domain measurement in this specific case is obvious; that is, the measurement results are not explicit in term of edge rate or skew rate, which are the jargons used by digital circuit designer. However this setback can be resolved by extraction of a spice model which will be mentioned latter in this paper [2].

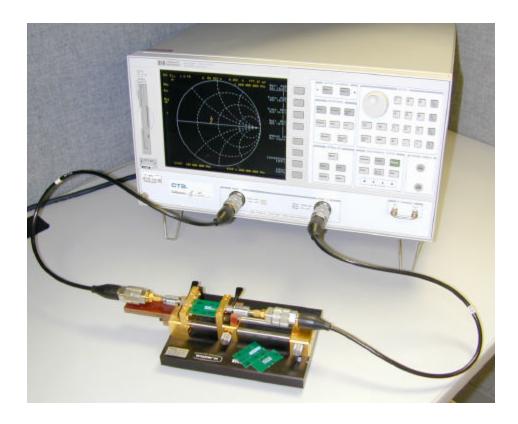

The TRL measurement scheme includes the following steps: design and fabrication of test PCB/test fixture, design and fabrication of TRL calibration standards, measurement and data processing. To ensure the measurement accuracy, special attention should be placed on the calibration standard fabrication accuracy and test fixture accuracy, as they are key steps. Ideally the test PCB and TRL calibration standards material properties should be accurately known. Since FR4 has a wide range of dielectric constant variation, it is not an ideal material for accurate measurements. But the shortcomings of FR4 materials can be overcome by fabricating calibration standards on the same test PCB and characterizing the properties of the test PCB material. In the measurements presented in this paper, the test PCB trace width was carefully selected to ensure the difference from the calibration standards line width was less than 0.5 mil. Another consideration was that the calibration standards design should be de-embedded from the trace and impedance discontinuity effects in the test fixture. This consideration has the following two effect: i)The calibration standards are designed to de-embedding the test PCB trace. ii) The Microstrip line impedance was chosen as close as possible to the resistance value of resistor network to be measured to minimize the measurement error. Figure 1 shows the measurement

setup and BGA resistor installed on a test PCB/fixture. An Agilent 8753E network analyzer with TRL calibration capability was used for the s parameter extraction.

Figure1

Resistor Network Measurement Setup

Generally speaking, the s parameters should be measured as an n port network and the resistor network then should be modeled as an n port network for its equivalent circuit [1]. A Y or Z matrix then can be derived from the knowledge of n port s parameters [3]. However, based on the fact that the coupling between two adjacent ones is dominant (S21 is below -40 to -50 dB at the low frequency end and -22dB to -42 dB at the high frequency end), the coupling between two resistors further apart can then be neglected. Therefore a  $\pi$  network can be used to model the two adjacent resistors. Under this assumption measurement work can be greatly reduced.

The resistor networks under test are installed on a test PCB in pairs to form  $\pi$  type circuits with a common ground. Two port measurements are carried out with the average factor set to 16, and the IF bandwidth equal to 3700Hz. The network analyzer frequency span is set from 100MHz to 1280MHz. S parameters are converted into equivalent circuits by means of conventional S-Y parameter conversion.

Another significant step in frequency domain measurements is to derive the equivalent circuits in a wide frequency span. Therefore time domain and frequency domains can be bridged with resistor network spice model developed. This transformation can be carried out as follows:

- i) Extract equivalent circuits from s parameters at discrete frequency points.

- ii) Extract equivalent circuits at certain frequency span, for example 100MHz to 1280MHz for the resistor network characterization.

- iii) Use an ADS linear simulator for fine tuning and verification of the equivalent circuit.

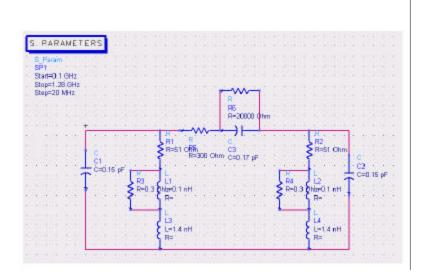

Figure 2

51 W BGA (CTS 73510J022) Resistor Network Equivalent Circuit

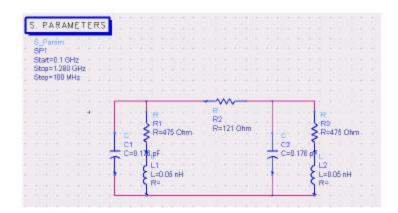

Samples of 5 different CTS resistor network part numbers were measured. Each resistance value had 10 samples and was measured on the set up as shown in Figure 1. The measured data were processed to derive the equivalent circuit. Figure 2 and Figure 3 show the equivalent circuit of a  $51\Omega$  BGA termination resistor network and a LVD SCSI termination resistor network.

Figure 3

LVD SCSI BGA (CTS RT1300EV, T1) Termination Resistor Network Equivalent Circuit

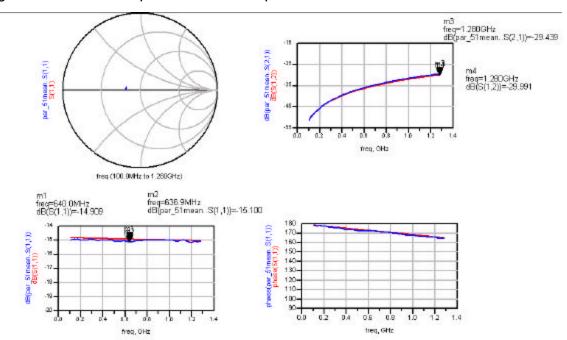

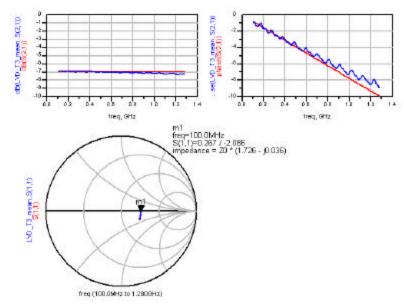

Figure 4 and Figure 5 show the comparison of equivalent circuit simulations and measured s parameter results of the 51  $\Omega$  BGA resistor network and LVS SCSI BGA termination resistors network respectively. It can be observed that satisfactory agreements between the s parameter and equivalent circuit simulation have been obtained.

In digital data transmission the parasitic parameters are of great interests because they may cause undesired skew, cross talk or jitter. The major BGA resistor network design goal is to reduce these parasitics. With the s parameter measurements and equivalent circuit derivation those parasitic parameters can be well characterized. The major parasitic parameters of various CTS BGA resistor networks are listed in Table 1.

Table 1

|                  | I/O<br>Inductance<br>(nH) | I/O<br>capacitance<br>(pF) | Coupling<br>Capacitance<br>of Two Adjacent<br>Resistors (pF) |

|------------------|---------------------------|----------------------------|--------------------------------------------------------------|

| CTS<br>73220J022 | 1.5                       | 0.2                        | 0.6                                                          |

| CTS<br>71220G010 | 1.5 –1.7                  | 0.2                        | 1.5                                                          |

| CTS<br>73380J018 | 1.5                       | 0.2                        | 0.25                                                         |

| CTS<br>73510J018 | 1.5                       | 0.15                       | 0.17                                                         |

| CTS<br>RT1300EV  | 0.2                       | 0.22                       | 0.12                                                         |

The equivalent circuits are simulated with ADS to compare s parameters with measurement results. Good correlation has been reached between measurements and simulations. Figure 4 and Figure 5 are the examples of these comparisons.

51 Ohm isolated measurement results and equivalent circuit simulation comparison

Figure 4

51W BGA Resistor Network (CTS73510J022) Simulation and Measurement Comparison

LVD T3 measurement results and equivalent simulation comparison

# Figure 5 LVD SCSI BGA Termination Resistor Network (CTS RT1300EV) Simulation and Measurement Comparison.

The results presented in this paper show good agreement between the measurement and simulation methods of model extraction. Which suggests that high-speed digital prototype circuits and production digital/analog circuits may be verified in the frequency domain by extraction of a spice model. It follows from these results that reliable results can be generated in the frequency domain using spice model extraction with recent software package developments and programs used in high frequency simulation, simulation of transmission lines, and interconnections. With the aid of these simulation tools and proper modeling of the circuits, digital circuit hardware development cycles should be shortened.

The next question to answer is how does this next generation low inductance and capacitance BGA SCSI terminator fit into the next generation of SCSI technology? Where we will soon be seeing U320 (Ultra4) LVD SCSI with a data rate of 320 MB/sec (Mega-byte/sec), double data clocking, bus training with different pre and post compensation voltages and current driver schemes along with smart active adaptive filtering schemes and technologies. U640 SCSI (Ultra5) is between 2 and 4 years away. What will be the effects of parasitics and the inherent packaging characteristics on the U640 generation of SCSI?

The following figures begin to give some indication of the importance of being able to extract equivalent circuit parameters at different frequencies for modeling purposes as SCSI speeds continue to climb. Using models generated using these techniques we should be able to address these questions to arrive at answers that will be needed as the technology continues to move forward.

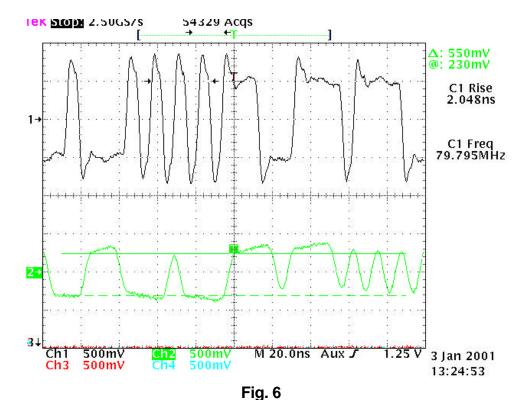

Output Waveforms (Ch1, Ch2) at Beginning and End of 25m Cable with Precomp Disabled, at Nominal Drive Strength and Slew Rate Settings

(12mA Assertion, 8mA Negation, 1.9ns).

Fig 7

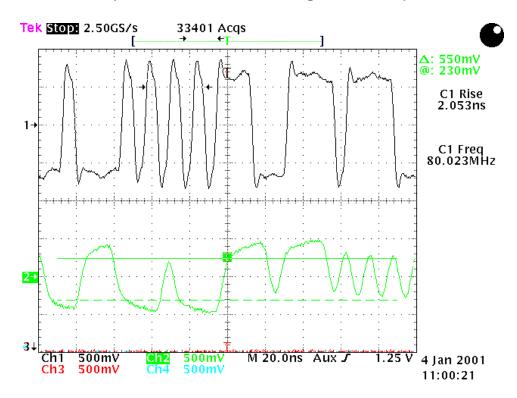

Output Waveforms (Ch1, Ch2) at Beginning and End of 25m Cable with Precomp Enabled, with LVD Signaling Set Up for Nominal Drive Strength and Slew Rate (10mA Assertion, 6mA Negation, 1.9ns).

Note: The Improvement in the Leveling out of the Far End Signal (Ch. 2).

Fig 8

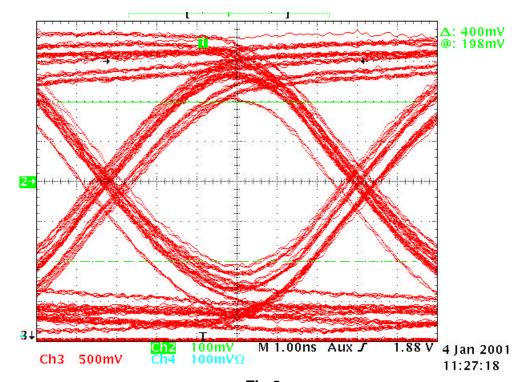

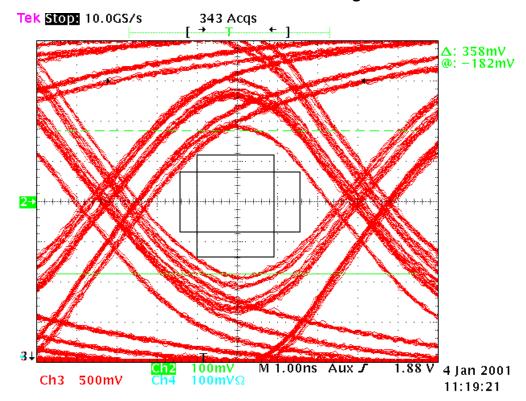

Eye Diagram of DB9 (Databit9) at Far End of 25m Cable with Pre-Emphasis

Disabled and Nominal Settings.

Fig 9

Eye Diagram of DB9 at Far End Of 25m Cable with Pre-Emphasis

Enabled and Nominal Settings

Generally in digital circuit design which the current and future SCSI technologies fall under, empirical formulas describing the circuit characteristics are frequently used. Those formulas are generally frequency independent and lack accuracy. As digital system speeds and particularly SCSI bus speeds steadily climb higher good agreement between the measured and simulation results are needed. Results presented in this paper suggest that the high-speed prototype circuits performance may be predicted by extraction of it spice models from frequency domain.

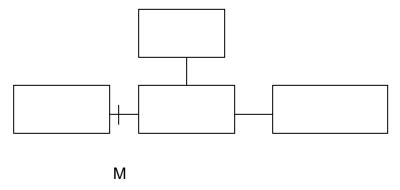

As an example of what could be done about the termination device, we suggest that a preferable termination, i.e. a preferable reflection, can be obtained with a certain match circuit if a target refection coefficient looking into the data bus at M is known,

The remaining issue is to know what are the s parameters at the network connection for a certain match circuit and termination device. The network S parameters can be derived as

$$S_{ep} = S_{pp} + S_{pc} (I - S_{cc})^{-1} S_{cp}$$

Where  $S_{ep}$  is the S parameter matrix of external and internal ports of overall system.  $S_{pp}$   $S_{cp}$ ,  $S_{pc}$  and  $S_{cc}$  are the s parameter matrix from circuit blocks. I is the internal ports connection matrix.

$$I = \begin{bmatrix} 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \\ 0 & 1 & 0 & 0 \\ 1 & 0 & 0 & 0 \end{bmatrix}$$

With recent developments of software packages used in high frequency simulation, simulation of a transmission lines and interconnections can generate reliable s parameters in the frequency domain.  $S_{pp}$   $S_{cp}$ ,  $S_{pc}$  and  $S_{cc}$  can be obtained from simulation results of the design. After  $S_{ep}$  is calculated, the spice model can be derived and time domain results can be obtained. Because the circuit can be simulated before real prototype devices are fabricated, a more accurate design is expected. This approach should greatly shorten the cut and try process of the digital circuit hardware development cycles. This is one of the author's experiences that by means of electromagnetic simulation a termination device high frequency performance can be predicted at a prototype design phase with good accuracy. It is also believed that this frequency domain to time domain approach can be applicable to termination/data bus design with many aspects of superiority over time domain approach.

#### References

- [1] 'VNA based system tests differential components" Vahe Adamian and Brad Cole, Microwaves & RF, March 2000.

- [2] 'Specifying calibration standards for the HP 8510 network analyzer" Agilent Application notes 8510-5A

- [3] 'Computer Aided Design of Microwave Circuits" K.C.Gupta, Ramesh Garg and Rakesh Ghadha. Artech House 1981.

- [4] 'Digital Signal Integrity' Brain Young, Prentice Hall © 2001.

- [5] 'Physical Design Rules for SCSI at GHz speed" Barry Caldwell, et al.